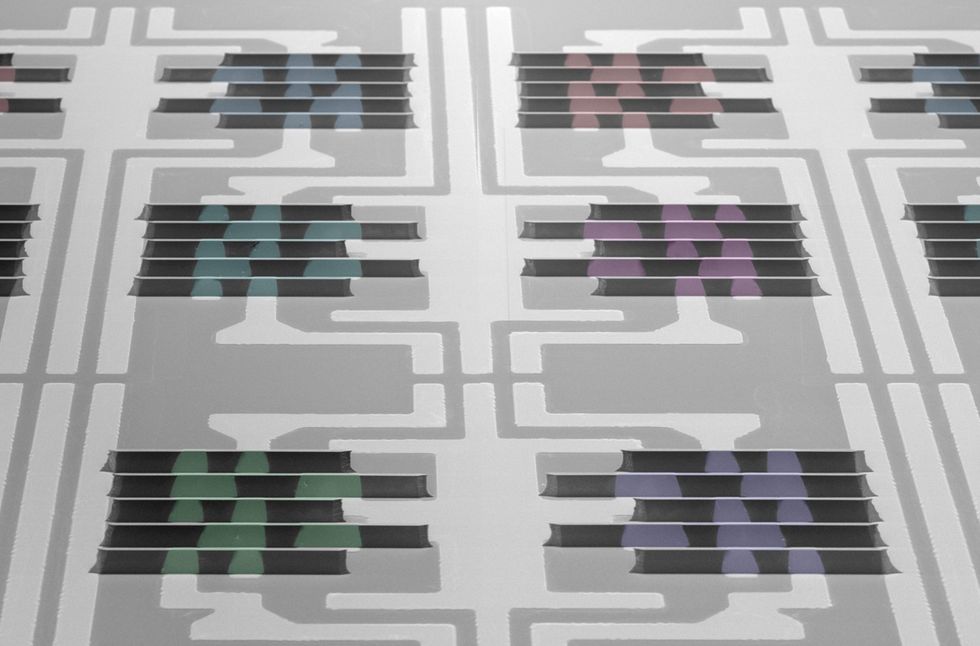

Los teléfonos inteligentes tienen un problema de escala. Específicamente, los filtros de radiofrecuencia (RF) que cada teléfono (y cada dispositivo inalámbrico en general) utiliza para extraer información de señales inalámbricas aisladas son demasiado grandes, demasiado planos y demasiado numerosos. Y sin estos filtros, las comunicaciones inalámbricas simplemente no funcionarían en absoluto. «Son literalmente la columna vertebral de los sistemas inalámbricos», dice Roozbeh Tabrizian, investigador de la Universidad de Florida en Gainesville. Por eso Tabrizian y otros investigadores de la Universidad de Florida ha desarrollado ahora un filtro de RF tridimensional alternativo que puede ahorrar espacio en teléfonos inteligentes y dispositivos IoT. Si algún día estos filtros 3D reemplazan las voluminosas pilas de filtros 2D, dejarían más espacio para otros componentes, como las baterías. También podrían facilitar la introducción de comunicaciones inalámbricas en frecuencias de terahercios, un importante rango de espectro que se está investigando para las tecnologías celulares 6G. “Muy pronto, tendremos billones de dispositivos conectados a redes inalámbricas y se necesitan nuevas bandas: solo necesitas toda una gama de frecuencias y toda una gama de filtros”. —Roozbeh Tabrizian, Universidad de Florida Los filtros que utilizan actualmente los dispositivos inalámbricos se denominan resonadores piezoeléctricos planos. Cada resonador tiene un grosor diferente: el grosor específico de un resonador está directamente relacionado con la banda de frecuencias inalámbricas a las que responde el resonador. Cualquier dispositivo inalámbrico que dependa de múltiples bandas de espectro (cada vez más común en la actualidad) requiere cada vez más de estos resonadores planos. Pero la tecnología de resonadores planos ha revelado una serie de debilidades a medida que proliferan las señales inalámbricas y se amplía el espectro en el que se basan esas señales. Una es que cada vez es más difícil hacer que los filtros sean lo suficientemente delgados para las nuevas franjas de espectro que los investigadores inalámbricos están interesados en aprovechar para las comunicaciones de próxima generación. Otro tiene que ver con el espacio. Cada vez resulta más difícil incluir todos los filtros de señal necesarios en los dispositivos. Las aletas verticales para los resonadores de aletas de puerta ferroeléctrica se pueden construir de la misma manera que los semiconductores FinFET. Faysal Hakim/Roozbeh Tabrizian/Universidad de Florida“Muy pronto, Tendrás billones de dispositivos conectados a redes inalámbricas y necesitarás nuevas bandas: sólo necesitas una amplia gama de frecuencias y una amplia gama de filtros”, afirma Tabrizian. “Si abres un celular, hay cinco o seis frecuencias específicas y listo. Cinco o seis frecuencias no pueden soportar eso. Es como si tuvieras cinco o seis calles y ahora quisieras acomodar el tráfico de una ciudad de 10 millones de habitantes”. Para cambiar a un filtro 3D, Tabrizian y sus colegas investigadores tomaron una página de otra industria que hizo el salto a la tercera dimensión: los semiconductores. Cuando, en la búsqueda continua por reducir el tamaño de los chips, parecía que la industria finalmente podría estar llegando al final del camino, un nuevo enfoque que elevó los canales de electrones por encima del sustrato semiconductor dio nueva vida a la Ley de Moore. El diseño del chip se llama FinFET (por “transistor de efecto de campo de aleta”, donde “aleta” se refiere al canal de electrones vertical similar a una aleta de tiburón). “El hecho de que podamos cambiar el ancho de la aleta juega un papel muy importante en haciendo que la tecnología sea mucho más capaz”. —Roozbeh Tabrizian, Universidad de Florida“Definitivamente nos inspiramos [by FinFETS]”, dice Tabrizian. «El hecho de que los transistores planos se convirtieran en aletas fue solo para garantizar que el tamaño efectivo del transistor fuera más pequeño y al mismo tiempo tuviera la misma área activa». A pesar de inspirarse en los FinFET, Tabrizian dice que existen algunas diferencias fundamentales en la forma en que las aletas verticales deben implementarse para los filtros de RF, en comparación con los chips. “Si piensas en FinFET, todas las aletas tienen casi el mismo ancho. La gente no cambia las dimensiones de la aleta”. No ocurre lo mismo con los filtros, que deben tener aletas de diferentes anchos. De esa manera, cada aleta del filtro se puede sintonizar a diferentes frecuencias, lo que permite que un filtro 3D procese múltiples bandas de espectro. «El hecho de que podamos cambiar el ancho de la aleta juega un papel muy importante a la hora de hacer que la tecnología sea mucho más capaz», dice Tabrizian. El grupo de Tabrizian ya ha fabricado múltiples filtros tridimensionales, llamados resonadores de aleta de puerta ferroeléctrica (FGF), que abarcaba frecuencias entre 3 y 28 gigahercios. También construyeron un procesador espectral compuesto por seis resonadores FGF integrados que cubrían frecuencias entre 9 y 12 GHz (a modo de comparación, el codiciado espectro de banda media de 5G se encuentra entre 1 y 6 GHz). Los investigadores publicaron su trabajo en enero en Nature Electronics. Aún es temprano para el desarrollo de filtros 3D, y Tabrizian reconoce que el camino por recorrer es largo. Pero, inspirándose nuevamente en los FinFET, ve un camino claro de desarrollo para los resonadores FGF. «La buena noticia es que ya podemos adivinar cuáles son muchos de estos desafíos al observar la tecnología FinFET», dice. Incorporar algún día resonadores FGF en dispositivos comerciales requerirá resolver varios problemas de fabricación, como descubrir cómo aumentar la densidad de aletas en el filtro y mejora de los contactos eléctricos. «Afortunadamente, como ya tenemos FinFET analizando muchas de estas respuestas, la parte de fabricación ya se está abordando», afirma Tabrizian. Una cosa en la que el grupo de investigación ya está trabajando es en el kit de diseño de procesos, o PDK, para resonadores FGF. Los PDK son comunes en la industria de los semiconductores y funcionan como una especie de guía para que los diseñadores fabriquen chips basados en componentes detallados por una fundición de chips. Tabrizian también ve un gran potencial para que la fabricación futura integre resonadores y semiconductores FGF en un solo componente. dadas sus similitudes en diseño y fabricación. «Es innovación y creatividad humana idear nuevos tipos de arquitecturas, que pueden revolucionar la forma en que pensamos sobre los resonadores, filtros y transistores». Artículos de su sitioArtículos relacionados en la Web

Source link

Etiqueta: diseño de chips

![]()

Se avecina el fin de la Ley de Moore. Los ingenieros y diseñadores sólo pueden hacer mucho para miniaturizar los transistores y empaquetar tantos como sea posible en chips. Por eso están recurriendo a otros enfoques para el diseño de chips, incorporando tecnologías como la IA en el proceso. Samsung, por ejemplo, está añadiendo IA a sus chips de memoria para permitir el procesamiento en la memoria, ahorrando así energía y acelerando el aprendizaje automático. Hablando de velocidad, el chip TPU V4 AI de Google ha duplicado su poder de procesamiento en comparación con el de su versión anterior. Pero la IA encierra aún más promesa y potencial para la industria de los semiconductores. Para comprender mejor cómo la IA revolucionará el diseño de chips, hablamos con Heather Gorr, gerente senior de productos de la plataforma MATLAB de MathWorks. ¿Cómo se utiliza actualmente la IA para diseñar la próxima generación de chips? Heather Gorr: La IA es una tecnología tan importante porque está involucrado en la mayor parte del ciclo, incluido el proceso de diseño y fabricación. Aquí hay muchas aplicaciones importantes, incluso en la ingeniería de procesos general donde queremos optimizar las cosas. Creo que la detección de defectos es importante en todas las fases del proceso, especialmente en la fabricación. Pero incluso pensando en el futuro en el proceso de diseño, [AI now plays a significant role] cuando estás diseñando la luz y los sensores y todos los diferentes componentes. Hay mucha detección de anomalías y mitigación de fallas que realmente desea considerar. Heather GorrMathWorks Luego, pensando en el modelado logístico que se ve en cualquier industria, siempre hay un tiempo de inactividad planificado que desea mitigar; pero también terminas teniendo un tiempo de inactividad no planificado. Entonces, mirando hacia atrás en los datos históricos de cuando ha tenido esos momentos en los que tal vez tomó un poco más de tiempo de lo esperado fabricar algo, puede echar un vistazo a todos esos datos y usar IA para tratar de identificar la causa próxima o para ver algo que pueda destacar incluso en las fases de procesamiento y diseño. A menudo pensamos en la IA como una herramienta predictiva o como un robot que hace algo, pero muchas veces se obtiene mucha información de los datos a través de la IA. ¿Cuáles son los beneficios de usar la IA para el diseño de chips? Gorr: Históricamente, He visto muchos modelos basados en la física, que es un proceso muy intensivo. Queremos hacer un modelo de orden reducido, donde en lugar de resolver un modelo tan extenso y costoso desde el punto de vista computacional, podamos hacer algo un poco más barato. Se podría crear un modelo sustituto, por así decirlo, de ese modelo basado en la física, utilizar los datos y luego realizar los barridos de parámetros, las optimizaciones y las simulaciones de Monte Carlo utilizando el modelo sustituto. Esto requiere mucho menos tiempo computacional que resolver directamente las ecuaciones basadas en la física. Entonces, estamos viendo ese beneficio de muchas maneras, incluida la eficiencia y la economía que son los resultados de iterar rápidamente los experimentos y las simulaciones que realmente ayudarán en el diseño. Entonces, ¿es como tener un gemelo digital en cierto sentido? Gorr : Exactamente. Eso es más o menos lo que la gente está haciendo, donde tienes el modelo del sistema físico y los datos experimentales. Luego, en conjunto, tienes este otro modelo que puedes modificar y ajustar y probar diferentes parámetros y experimentos que te permitan analizar todas esas situaciones diferentes y llegar a un mejor diseño al final. Por lo tanto, será más eficiente. y, como dijiste, ¿más barato? Gorr: Sí, definitivamente. Especialmente en las fases de experimentación y diseño, donde intentas cosas diferentes. Obviamente, esto generará importantes ahorros de costos si realmente estás fabricando y produciendo. [the chips]. Quiere simular, probar y experimentar tanto como sea posible sin crear algo utilizando la ingeniería de procesos real. Hemos hablado de los beneficios. ¿Qué hay de los inconvenientes? Gorr: El [AI-based experimental models] tienden a no ser tan precisos como los modelos basados en la física. Por supuesto, es por eso que se hacen muchas simulaciones y barridos de parámetros. Pero ese también es el beneficio de tener ese gemelo digital, donde puedes tenerlo en cuenta: no será tan preciso como ese modelo preciso que hemos desarrollado a lo largo de los años. Tanto el diseño como la fabricación del chip requieren un uso intensivo del sistema; Tienes que considerar cada pequeña parte. Y eso puede ser realmente un desafío. Es un caso en el que es posible que tengas modelos para predecir algo y diferentes partes de ello, pero aun así necesitas unirlo todo. Una de las otras cosas en las que pensar también es que necesitas los datos para construir los modelos. Tienes que incorporar datos de todo tipo de sensores diferentes y diferentes tipos de equipos, y eso aumenta el desafío. ¿Cómo pueden los ingenieros usar la IA para preparar y extraer mejor información de los datos del hardware o de los sensores? Gorr: Siempre pensamos en usar la IA para predecir algo o realizar alguna tarea de robot, pero puedes usar la IA para crear patrones y seleccionar cosas que quizás no hayas notado antes por tu cuenta. Las personas usarán IA cuando tengan datos de alta frecuencia provenientes de muchos sensores diferentes, y muchas veces es útil explorar el dominio de la frecuencia y cosas como la sincronización o el remuestreo de datos. Esto puede ser un verdadero desafío si no está seguro de por dónde empezar. Una de las cosas que yo diría es que utilice las herramientas disponibles. Hay una gran comunidad de personas trabajando en estas cosas y puedes encontrar muchos ejemplos. [of applications and techniques] en GitHub o MATLAB Central, donde las personas han compartido buenos ejemplos, incluso pequeñas aplicaciones que han creado. Creo que muchos de nosotros estamos sumergidos en datos y simplemente no estamos seguros de qué hacer con ellos, así que definitivamente aproveche lo que ya existe en la comunidad. Puede explorar y ver qué tiene sentido para usted, y aportar ese equilibrio entre el conocimiento del dominio y la información que obtiene de las herramientas y la IA. ¿Qué deberían considerar los ingenieros y diseñadores al utilizar la IA para el diseño de chips? Gorr: Piense en los problemas que enfrenta. estás tratando de resolver o qué ideas esperas encontrar, y trata de ser claro al respecto. Considere todos los diferentes componentes, documente y pruebe cada una de esas partes diferentes. Considere a todas las personas involucradas, explique y transmítalas de una manera que sea sensata para todo el equipo. ¿Cómo cree que la IA afectará los trabajos de los diseñadores de chips? Gorr: Liberará una gran cantidad de capital humano para personal más avanzado. tareas. Podemos usar la IA para reducir el desperdicio, optimizar los materiales, optimizar el diseño, pero aún así tienes a ese ser humano involucrado cuando se trata de la toma de decisiones. Creo que es un gran ejemplo de personas y tecnología trabajando de la mano. También es una industria en la que todas las personas involucradas, incluso en la planta de fabricación, necesitan tener cierto nivel de comprensión de lo que está sucediendo, por lo que esta es una gran industria para hacer avanzar la IA debido a cómo probamos las cosas y cómo pensamos sobre ellas antes de ponerlas a prueba. ¿Cómo imagina el futuro de la IA y el diseño de chips? Gorr: Depende en gran medida de ese elemento humano: involucrar a las personas en el proceso y tener ese modelo interpretable. Podemos hacer muchas cosas con las minucias matemáticas del modelado, pero todo se reduce a cómo lo usan las personas, cómo todos en el proceso lo entienden y aplican. La comunicación y la participación de personas de todos los niveles en el proceso serán realmente importantes. Veremos menos de esas predicciones superprecisas y más transparencia en la información, el intercambio y ese gemelo digital, no solo usando IA sino también nuestro conocimiento humano y todo el trabajo que muchas personas han hecho a lo largo de los años. Artículos del sitioArtículos relacionados en la Web

Source link

En un discurso de apertura en la Conferencia Internacional IEEE/ACM sobre Diseño Asistido por Computadora el lunes, el director de tecnología de Nvidia, Bill Dally, reveló que la compañía ha estado probando un modelo de IA en lenguaje grande para aumentar la productividad de sus diseñadores de chips. los hicimos un 5 por ciento más productivos, eso es una gran victoria”, dijo Dally en una entrevista antes de la conferencia. Nvidia no puede afirmar que haya alcanzado ese objetivo todavía. El sistema, llamado ChipNeMo, no está preparado para el tipo de prueba grande (y prolongada) que realmente demostraría su valor. Pero un grupo de voluntarios de Nvidia lo está utilizando y hay algunos indicios positivos, afirmó Dally. ChipNeMo es una versión especialmente adaptada de un modelo de lenguaje grande. Comienza como un LLM compuesto por 43 mil millones de parámetros que adquiere sus habilidades a partir de un billón de tokens (unidades lingüísticas fundamentales) de datos. «Eso es como darle una educación en artes liberales», dijo Dally. «Pero si quieres enviarlo a la escuela de posgrado y especializarlo, debes ajustarlo en un corpus de datos particular… en este caso, el diseño de chips». Eso requirió dos pasos más. Primero, ese modelo ya entrenado se volvió a entrenar con 24 mil millones de tokens de datos especializados. Doce mil millones de esos tokens provinieron de documentos de diseño, informes de errores y otros datos internos en inglés acumulados durante los 30 años de trabajo de Nvidia en el diseño de chips. Los otros 12 mil millones de tokens provinieron de código, como el lenguaje de descripción de hardware Verilog y scripts para llevar a cabo cosas con herramientas de automatización de diseño electrónico industrial (EDA). Finalmente, el modelo resultante se sometió a un “ajuste supervisado”, entrenándose en 130.000 conversaciones y diseños de muestra. Al resultado, ChipNeMo, se le asignaron tres tareas diferentes: como chatbot, como guionista de la herramienta EDA y como resumidor. de informes de errores. Actuar como un chatbot para ingenieros podría ahorrar tiempo a los diseñadores, dijo Dally. «Los diseñadores senior dedican mucho tiempo a responder preguntas de los diseñadores junior», dijo. Como chatbot, la IA puede ahorrar tiempo al diseñador senior respondiendo preguntas que requieren experiencia, como qué podría significar una señal extraña o cómo se debe ejecutar una prueba específica. Sin embargo, los chatbots son conocidos por su disposición a mentir cuando no lo hacen. conocen la respuesta y su tendencia a alucinar. Entonces, los desarrolladores de Nvidia integraron una función llamada generación aumentada de recuperación en ChipNeMo para mantenerlo en el nivel. Esa función obliga a la IA a recuperar documentos de los datos internos de Nvidia para respaldar sus sugerencias. La incorporación de la generación de recuperación aumentada «mejora bastante la precisión», dijo Dally. «Más importante aún, reduce las alucinaciones». En su segunda aplicación, ChipNeMo ayudó a los ingenieros a realizar pruebas en diseños y partes de ellos. «Utilizamos muchas herramientas de diseño», dijo Dally. «Estas herramientas son bastante complicadas y normalmente implican muchas líneas de secuencias de comandos». ChipNeMo simplifica el trabajo del diseñador al proporcionar una «interfaz humana muy natural para lo que de otro modo serían comandos muy arcanos». El caso de uso final de ChipNeMo, que analiza y resume los informes de errores, «es probablemente aquel en el que vemos las perspectivas de mayor aumento de productividad». lo antes posible”, dijo Dally. Cuando una prueba falla, explicó, se registra en el sistema interno de informe de errores de Nvidia, y cada informe puede incluir páginas y páginas de datos detallados. Luego se envía un «ARB» (abreviatura de «acción requerida por») a un diseñador para que lo solucione, y el tiempo comienza a correr. ChipNeMo resume las muchas páginas del informe de error en tan solo un párrafo, lo que acelera las decisiones. Incluso puede escribir ese resumen en dos modos: uno para el ingeniero y otro para el gerente. Los fabricantes de herramientas de diseño de chips, como Synopsys y Cadence, se han sumergido en la integración de la IA en sus sistemas. Pero según Dally, no podrán lograr lo mismo que Nvidia busca. “Lo que nos permite hacer esto son 30 años de documentos de diseño y código en una base de datos”, dijo. ChipNeMo está aprendiendo «de toda la experiencia de Nvidia». Las empresas de EDA simplemente no tienen ese tipo de datos. Artículos de su sitio Artículos relacionados en la Web

Source link